# A Study on the Increasing Trend of Electronic Chips in Industry

Girija.G. Mangalagatti

Assistant Professor Department Of Electronics Government First Grade College, Bidar, Karnataka

### Abstract

Intricacy of integrated circuits has roughly multiplied each year since their presentation. Cost per function has diminished a few thousand-overlay, while framework execution and dependability have been improved significantly. Numerous parts of handling and plan innovation have added to make the production of such functions as perplexing single chip microchips or memory circuits monetarily plausible. It is feasible to break down the increment in intricacy into various elements that can, thusly, be inspected to perceive which commitments have been significant in this development and how they may be required to keep on advancing. The normal patterns can be recombined to perceive how long exponential growth in intricacy can be required to proceed. The current paper highlights the increasing trend of electronic chips in industry. **Keywords:** Electronic, Chip, Power

## I. Introduction

The semiconductor chips structure the center of a force electronic module. Fig.1 shows the inside of a force electronic module with semiconductor chips mounted on a DBC substrate and interconnected with wire bonds. Semiconductor chips decide the voltage, current, and force evaluations of the force module. Force modules with various inner interconnections of semiconductor chips are accessible to acknowledge diverse force converter geographies like half scaffold and full extension. To accomplish high-current capacity, different semiconductor chips can be resembled inside the module. The exhibition of force modules as far as on-opposition, exchanging rate, and force misfortune is basically subject to the semiconductor chip attributes.

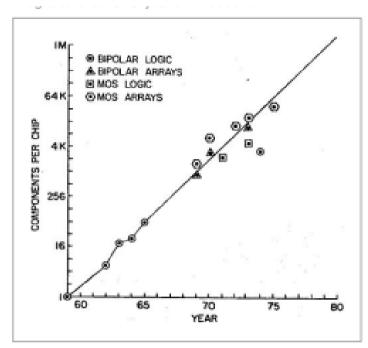

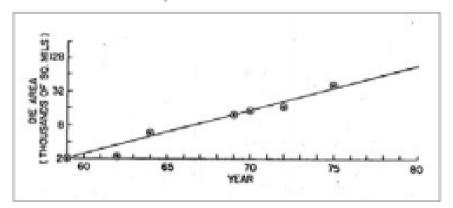

A first factor is the region of the integrated designs. Chip zones for probably the biggest of the circuits utilized in developing Figure 1 are plotted in Figure 2. Here once more, the pattern follows an exponential very well, yet with essentially lower slant than the intricacy curve. Chip territory peak greatest intricacy has expanded by a factor of around 20 from the main planar transistor in 1959 to the 16,384-bit charge-coupled gadget memory chip that compares to the point plotted for 1975, while intricacy, as indicated by the annual multiplying law, ought to have expanded around 65,000-overlap. Plainly a significant part of the expanded intricacy needed to result from higher density of segments on the chip, as opposed to from the expanded region accessible using bigger chips.

Figure 1 Approximate component count for complex integrated circuits vs. year of Introduction

Figure 2 Increase in die area for most complex integrated devices commercially available

# INCREASING TREND OF ELECTRONIC CHIPS IN INDUSTRY

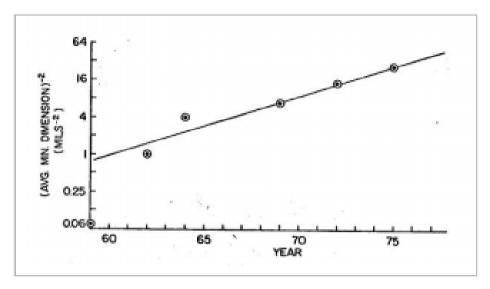

Density was expanded in part by utilizing better scale microstructures. The initially integrated circuits of 1961 utilized line widths of 1 mil (~25 micrometers) while the 1975 gadget utilizes 5 micrometer lines. Both line width and dispersing between lines are similarly significant in improving density. Since they have not generally been equivalent, the normal of the two is a decent boundary to identify with the zone that a construction may involve. Density can be required to be corresponding to the proportional of territory, so the commitment to improve density versus time from the utilization of more modest dimensions is plotted in Figure 3.

Dismissing the main planar transistor, where moderate line width and dividing was utilized, there is again a sensible fit to an exponential growth. From the exponential guess addressed by the straight line in Figure 3, the expansion in density from this source over the 1959-1975 period is a factor of roughly 32.

Figure 3 Device density contribution from the decrease in line widths and spacings.

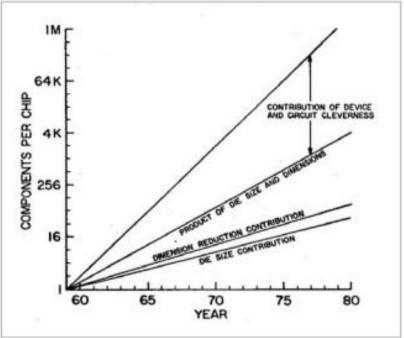

Consolidating the commitment of bigger chip region and higher density coming about because of calculation represents a 640-overlap expansion in intricacy, leaving a factor of around 100 to represent through 1975, as is shown graphically in Figure 4.

This factor is the commitment of circuit and gadget advances to higher density. It is critical that this commitment to intricacy has been a higher priority than either expanded chip territory or better lines. Progressively the surface regions of the integrated gadgets have been focused on parts instead of to such idle constructions as gadget separation and interconnections, and the actual segments have moved toward least size, reliable with the dimensional resistances utilized.

Figure 4 Decomposition of the complexity curve into various components.

#### II. Discussion

Extrapolating the curve for bite the dust size to 1980 recommends that chip territory may be around 90,000 sq. mils, or what might be compared to 0.3 inches square. Such a kick the bucket size is unmistakably reliable with the 3 inch wafer as of now broadly utilized by the industry. Indeed, the size of the actual wafers have become probably as quick as has bite the dust size during the time span viable and can be relied upon to keep on developing.

Augmentation to bigger bite the dust size relies chiefly on the proceeded with decrease in the density of deformities. Since the presence of the kind of imperfections that damage integrated circuits isn't major, their density can be diminished as long as such decrease has adequate financial legitimacy to legitimize the exertion.

Regarding dimensions, in these perplexing gadgets we are still a long way from the base gadget sizes restricted by such key contemplations as the charge on the electron or the atomic design of issue. Discrete gadgets with sub-micrometer dimensions show that no fundamental issues ought normal at any rate until the normal line width and spaces are a micrometer or less. This takes into consideration an extra factor of progress at any rate equivalent to the commitment from the better calculations of the most recent fifteen years.

Work in non-optical concealing methods, both electron bar and X-beam, proposes that the necessary goal capacities will be accessible. Much work is needed to be certain that imperfection densities keep on improving as gadgets are scaled to exploit the improved goal. Be that as it may, I see no motivation to anticipate the rate of progress in the utilization of more modest least dimensions in complex circuits to diminish soon. This contribution should continue along the curve of Figure 3.

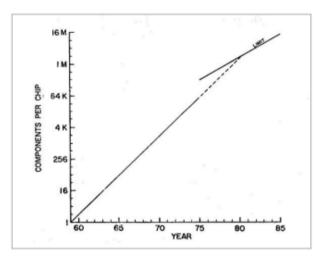

Figure 5 Projection of the complexity curve reflecting the limit on increased density through invention.

With respect to the factor contributed by device and circuit cleverness, however, the situation is different. Here we are approaching a limit that must slow the rate of progress. The CCD structure can approach closely the maximum density practical.

This structure requires no contacts to the components within the array, but uses gate electrodes that can be at minimum spacing to transfer charge and information from one location to the next. Some improvement in overall packing efficiency is possible beyond the structure plotted as the 1975 point in Figure 1, but it is unlikely that the packing efficiency alone can contribute as much as a factor of four, and this only in serial data paths.

#### III. Conclusion

With this factor disappearing as an important contributor, the rate of increase of complexity can be expected to change slope in the next few years as shown in Figure 5. The new slope might approximate a doubling every two years, rather than every year, by the end of the decade.

Even at this reduced slope, integrated structures containing several million components can be expected within ten years. These new devices will continue to reduce the cost of electronic functions and extend the utility of digital electronics more broadly throughout society.

#### References

- S. Wolf and R.N. Tauber, Silicon processing for the VLSI era- Vol.1 Process Technology, (Lattice Press, Sunset Beach, CA, 2016), p.603

- [2]. M.H. Kibel and P.W. Leech, Surface and Interface Analysis, 24, 605, (2016)

- [3]. A.E. Morgan: in Characterisation of semiconductor materials: principles and methods ed. by G.E. McGuire, (Noyes Publications, NJ, 2014), 49

- [4]. C.J. Palmstrom, and D.V. Morgan, in Gallium Arsenide, Materials, Devices and Circuits, Eds. M.J. Howes and D.V. Morgan, (J. Wiley and Sons), 195, (2015)

- [5]. P.W. Leech, G.K. Reeves, W. Zhou and P. Ressel, J. Vac. Sci. Techno!., B16(1), 227, (2016)

- [6]. J. Herniman, J.S. Yu and A.E. Staton-Bevan, App!. Surf. Science, 52, 289, (2017)

- [7]. S.A. Schartz, M.A. Pudensi, T. Sands, T.J. Gmitter, R. Bhat, M. Koxza, L.C. Wang and S.S. Lau, Appl. Phys. Lett., 60(9), 1123, (2016)

- [8]. P. Ressel, P.W. Leech, P. Veit, E. Nebauer, A. Klein, E. Kuphal, G.K. Reeves and H.L. Hartnagel, J. Appl. Phys., 84(2), 861, (2018)